इलेक्ट्रॉनिक्स के क्षेत्र में, सबसे महत्वपूर्ण अवधारणा जो हर घटक पर काम करती है वह है ' तर्क द्वार “। जैसा कि लॉजिक गेट्स की अवधारणा हर कार्यक्षमता में एकीकृत सर्किट, सेंसर, स्विचिंग उद्देश्य, माइक्रोकंट्रोलर और प्रोसेसर, एन्क्रिप्शन और डिक्रिप्शन प्रयोजनों और अन्य में कार्यान्वित की जाती है। इनके अतिरिक्त लॉजिक गेट्स के व्यापक अनुप्रयोग हैं। कई प्रकार के लॉजिक गेट हैं जैसे कि एडडर, सबट्रैक्टर, फुल एडर , पूर्ण सबट्रैक्टर, हाफ सबट्रैक्टर, और कई अन्य। तो, यह लेख सामूहिक जानकारी प्रदान करता है आधा घटाव सर्किट , आधा घटाव सत्य तालिका , और संबंधित अवधारणाएँ।

हाफ सबट्रैक्टर क्या है?

आधे घटाव पर चर्चा करने से पहले, हमें बाइनरी घटाव को जानना होगा। बाइनरी घटाव में, घटाव की प्रक्रिया अंकगणितीय घटाव के समान है। अंकगणितीय घटाव में आधार 2 संख्या प्रणाली का उपयोग किया जाता है जबकि बाइनरी घटाव में, द्विआधारी संख्या का उपयोग घटाव के लिए किया जाता है। परिणामी शब्दों को अंतर और उधार के साथ दर्शाया जा सकता है।

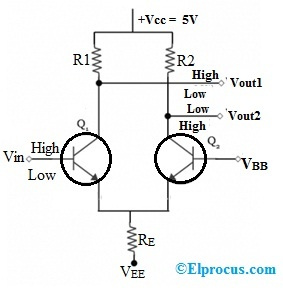

आधा घटाव सबसे आवश्यक है संयोजन तर्क सर्किट जिसका उपयोग किया जाता है डिजिटल इलेक्ट्रॉनिक्स । मूल रूप से, यह एक इलेक्ट्रॉनिक उपकरण है या अन्य शब्दों में, हम इसे तर्क सर्किट कह सकते हैं। इस सर्किट का उपयोग दो बाइनरी अंक घटाव करने के लिए किया जाता है। पिछले लेख में, हम पहले ही चर्चा कर चुके हैं आधे योजक और एक पूर्ण योजक सर्किट की अवधारणाएं जो गणना के लिए द्विआधारी संख्या का उपयोग करता है। इसी प्रकार, घटाव सर्किट घटाव के लिए द्विआधारी संख्या (0,1) का उपयोग करता है। आधा घटाव का सर्किट दो के साथ बनाया जा सकता है तर्क द्वार नंद और पूर्व या द्वार । यह सर्किट दो तत्वों को अंतर देता है जैसे कि वे उधार लेते हैं।

जैसा कि बाइनरी घटाव में, प्रमुख अंक 1 है, हम उधार ले सकते हैं जबकि सबट्रेंड 1 मिन्यूएड 0 से बेहतर है और इसके कारण, उधार की आवश्यकता होगी। निम्न उदाहरण दो बाइनरी बिट्स के द्विआधारी घटाव देता है।

पहला अंक | दूसरा अंक | अंतर | उधार |

० | ० | ० | ० |

1 | ० | 1 | ० |

| ० | 1 | 1 | 1 |

| 1 | 1 | ० | ० |

उपरोक्त घटाव में, दो अंकों को ए और बी के साथ दर्शाया जा सकता है। इन दो अंकों को घटाया जा सकता है और परिणामी बिट्स को अंतर और उधार के रूप में दिया जा सकता है।

जब हम पहली दो और चौथी पंक्तियों का निरीक्षण करते हैं, तो इन पंक्तियों के बीच का अंतर, फिर अंतर और उधार समान होता है क्योंकि सबट्रेंड मिनुएड की तुलना में कम होता है। इसी तरह, जब हम तीसरी पंक्ति का निरीक्षण करते हैं, तो सबटेंडेंड से घटाए गए मूल्य को घटा दिया जाता है। तो अंतर और उधार बिट्स 1 हैं, क्योंकि सबट्रेन्ड अंक मिनुइंड अंक से बेहतर है।

यह कॉम्बिनेशन सर्किट किसी भी तरह का एक अनिवार्य उपकरण है डिजिटल सर्किट इनपुट और आउटपुट के संभावित संयोजनों को जानना। उदाहरण के लिए, यदि सबट्रैक्टर में दो इनपुट हैं तो परिणामी आउटपुट चार होगा। आधे घटाव के ओ / पी का उल्लेख नीचे दी गई तालिका में किया गया है जो अंतर बिट के साथ-साथ उधार बिट को सूचित करेगा। सर्किट की सत्य सारणी का विवरण लॉजिक गेट जैसे EX-OR लॉजिक गेट और नॉट गेट गेट द्वारा संचालित ऑपरेशन का उपयोग करके किया जा सकता है।

सत्य तालिका का उपयोग करके हल करना कश्मीर का नक्शा नीचे दिखाया गया है।

आधा घटाव k नक्शा

आधा घटाव अभिव्यक्ति सत्य तालिका और के-मानचित्र का उपयोग कर के रूप में प्राप्त किया जा सकता है

अंतर (डी) = ( xyy + xy ')

= x ⊕ य

उधार (B) = x’y

तार्किक सर्किट

आधा घटाव तार्किक सर्किट तर्क द्वार का उपयोग करके समझाया जा सकता है:

- 1 XOR गेट

- 1 गेट नहीं

- 1 और गेट

प्रतिनिधित्व है

हाफ सबट्रैक्टर लॉजिकल सर्किट

आधा-घटाव ब्लॉक आरेख

आधा सबट्रैक्टर का ब्लॉक आरेख ऊपर दिखाया गया है। इसके लिए दो इनपुट की जरूरत होती है और साथ ही दो आउटपुट भी मिलते हैं। यहां इनपुट्स को ए और बी के साथ दर्शाया गया है, और आउटपुट में अंतर और उधार हैं।

उपरोक्त सर्किट को EX-OR & NAND गेट्स के साथ डिजाइन किया जा सकता है। यहाँ, NAND गेट का उपयोग AND और NOT गेट्स द्वारा किया जा सकता है। इसलिए हमें एक्स-या गेट, नॉट गेट, और एनएएनडी गेट को आधा सबट्रैक्टर सर्किट बनाने के लिए तीन लॉजिक गेट्स की आवश्यकता होती है।

AND और NOT गेट का एक संयोजन NAND गेट नामक एक अलग संयुक्त गेट का उत्पादन करता है। Ex-OR गेट आउटपुट अंतर बिट होगा और NAND गेट आउटपुट A & B समान इनपुट के लिए बॉरो बिट होगा।

और-गेट

AND-गेट एक प्रकार का डिजिटल लॉजिक गेट है जिसमें कई इनपुट और एक ही आउटपुट होता है और इनपुट कॉम्बिनेशन के आधार पर यह लॉजिकल कंजम्पशन करेगा। जब इस गेट के सभी इनपुट उच्च होंगे, तो आउटपुट अधिक होगा अन्यथा आउटपुट कम होगा। सच्चाई तालिका के साथ AND गेट का तर्क आरेख नीचे दिखाया गया है।

और गेट और सत्य तालिका

गेट नहीं

NOT-गेट एक प्रकार का डिजिटल लॉजिक गेट है जिसमें एक इनपुट होता है और इनपुट के आधार पर आउटपुट को उलट दिया जाएगा। उदाहरण के लिए, जब NOT गेट का इनपुट अधिक होता है तो आउटपुट कम होगा। सत्य तालिका के साथ NOT-गेट का तर्क आरेख नीचे दिखाया गया है। इस प्रकार के लॉजिक गेट का उपयोग करके, हम NAND और NOR गेट्स को निष्पादित कर सकते हैं।

गेट और ट्रुथ टेबल नहीं

पूर्व या गेट

एक्सक्लूसिव-ओर या EX-OR गेट एक प्रकार का डिजिटल लॉजिक गेट है जिसमें 2-इनपुट और सिंगल आउटपुट है। इस लॉजिक गेट का काम OR गेट पर निर्भर करता है। यदि इस गेट के इनपुट में से कोई भी उच्च है, तो EX-OR गेट का आउटपुट अधिक होगा। EX-OR का प्रतीक और सत्य तालिका नीचे दिखाई गई है।

XOR गेट और ट्रुथ टेबल

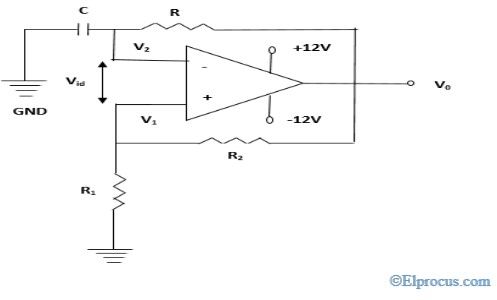

नंद गेट का उपयोग करते हुए आधा घटाव सर्किट

घटाव के डिजाइनिंग द्वारा किया जा सकता है तर्क द्वार का उपयोग करना नंद द्वार और पूर्व या द्वार की तरह। इस आधे सबट्रैक्टर सर्किट को डिजाइन करने के लिए, हमें अंतर और उधार दो अवधारणाओं को जानना होगा।

नंद गेट का उपयोग करते हुए आधा घटाव सर्किट

यदि हम सावधानी से निगरानी करते हैं, तो यह स्पष्ट है कि इस सर्किट द्वारा निष्पादित ऑपरेशन की विविधता जो सटीक रूप से EX-OR गेट ऑपरेशन से संबंधित है। इसलिए, हम केवल अंतर बनाने के लिए EX-OR गेट का उपयोग कर सकते हैं। उसी तरह, आधे योजक सर्किट द्वारा उत्पादित ऋण को AND- गेट और NOT-गेट जैसे तर्क गेट्स के मिश्रण का उपयोग करके प्राप्त किया जा सकता है।

इस HS को NOR गेट्स का उपयोग करके भी डिज़ाइन किया जा सकता है जहाँ निर्माण के लिए इसे 5 NOR द्वार की आवश्यकता होती है। NOR गेट्स का उपयोग करते हुए सर्किट आरेख आधा घटाव के रूप में दिखाया गया है:

नॉन गेट्स का उपयोग करके आधा घटाव

सच्ची तालिका

पहला बिट | दूसरा बिट | अंतर (पूर्व या बाहर) | उधार (नंद आउट) |

० | ० | ० | ० |

| 1 | ० | 1 | ० |

० | 1 | 1 | 1 |

| 1 | 1 | ० | ० |

वीएचडीएल और टेस्टबेंच कोड

आधे घटाव के लिए VHDL कोड इस प्रकार बताया गया है:

पुस्तकालय IEEE

IEEE.STD_LOGIC_1164.ALL का उपयोग करें

IEEE.STD_LOGIC_ARITH.ALL का उपयोग करें

IEEE.STD_LOGIC_UNSIGNED.ALL का उपयोग करें

संस्था Half_Sub1 है

पोर्ट (a: STD_LOGIC में)

b: STD_LOGIC में

HS_Diff: STD_LOGIC बाहर

HS_Borrow: STD_LOGIC के बाहर)

अंत Half_Sub1

आर्किटेक्चर बिहेवियरल ऑफ हाफ_सब 1 है

शुरू

HS_Diff<=a xor b

HS_B दुख<=(not a) and b

एचएस के लिए टेस्टबेंच कोड नीचे बताया गया है:

लिब्ररी IEEE

USE ieee.std_logic_1164.ALL

ENTITY HS_tb IS है

END HS_tb

वास्तुकला HS_tb का HS_tb IS है

घटक एच.एस.

PORT (a: std_logic में

b: std_logic में

HS_Diff: OUT std_logic

HS_Borrow: OUT std_logic

)

अंत घटक

संकेत: a: std_logic: =: 0 '

संकेत b: std_logic: = _ 0 '

संकेत HS_Diff: std_logic

संकेत HS_Breat: std_logic

शुरू

नया: एचएस पोर्ट एमएपी (

a => ए,

बी => बी,

HS_Diff => HS_Diff,

HS_borrow => HS_borrow

)

stim_proc: प्रक्रिया

शुरू

सेवा मेरे<= ‘0’

ख<= ‘0’

30 ns के लिए प्रतीक्षा करें

सेवा मेरे<= ‘0’

ख<= ‘1’

30 ns के लिए प्रतीक्षा करें

सेवा मेरे<= ‘1’

ख<= ‘0’

30 ns के लिए प्रतीक्षा करें

सेवा मेरे<= ‘1’

ख<= ‘1’

रुको

प्रक्रिया समाप्त

समाप्त

हाफ सबट्रैक्टर का उपयोग करके पूरा सबट्रैक्टर

एक पूर्ण सबट्रैक्टर एक कॉम्बीनेशन डिवाइस है जो दो बिट्स का उपयोग करके घटाव की कार्यक्षमता को संचालित करता है और मिनुएन्ड और सबट्रेंड है। सर्किट उधार को पिछले आउटपुट मानता है और इसमें दो आउटपुट के साथ तीन इनपुट हैं। तीन इनपुट मीनूएंड, सबट्रेंड और पिछले आउटपुट से प्राप्त इनपुट है जो उधार है और दो आउटपुट अंतर और उधार हैं।

पूर्ण सबट्रैक्टर तार्किक आरेख

के लिए सच्चाई तालिका पूर्ण घटाव है

| इनपुट | आउटपुट | |||

| एक्स | य | यिन | FS_Diff | FS_Borrow |

| ० | ० | ० | ० | ० |

| ० | ० | 1 | 1 | 1 |

| ० | 1 | ० | 1 | 1 |

| ० | 1 | 1 | ० | 1 |

| 1 | ० | ० | 1 | ० |

| 1 | ० | 1 | ० | ० |

| 1 | 1 | ० | ० | ० |

| 1 | 1 | 1 | 1 | 1 |

उपरोक्त सत्य तालिका के साथ, आधा सबट्रैक्टर का उपयोग करके पूर्ण सबट्रैक्टर के कार्यान्वयन के लिए तार्किक आरेख विज्ञापन सर्किट आरेख नीचे दिखाया गया है:

एचएस का उपयोग करके पूर्ण सबट्रैक्टर

हाफ सबट्रैक्टर के फायदे और सीमाएं

आधे घटाव के फायदे हैं:

- इस सर्किट का कार्यान्वयन और निर्माण सरल और आसान है

- यह सर्किट डिजिटल सिग्नल प्रोसेसिंग में न्यूनतम बिजली की खपत करता है

- कम्प्यूटेशनल फ़ंक्शंस को बेहतर गति दरों पर किया जा सकता है

इस कॉम्बिनेशन सर्किट की सीमाएँ हैं:

भले ही कई कार्यों और कार्यों में आधे घटाव के व्यापक अनुप्रयोग हैं, कुछ सीमाएँ हैं और वे हैं:

- आधा घटाव सर्किट पिछले आउटपुट से 'बॉरो-इन' को स्वीकार नहीं करेगा जहां यह इस सर्किट का महत्वपूर्ण दोष है

- कई वास्तविक समय के अनुप्रयोग कई बिट्स के घटाव पर काम करते हैं, आधे घटाव वाले उपकरण अपने बिट्स को घटाने की कोई क्षमता नहीं रखते हैं।

हाफ सबट्रैक्टर के अनुप्रयोग

आधे घटाव के अनुप्रयोगों में निम्नलिखित शामिल हैं।

- ऑडियो या रेडियो संकेतों के बल को कम करने के लिए आधा सबट्रैक्टर का उपयोग किया जाता है

- यह हो सकता है एम्पलीफायरों में उपयोग किया जाता है ध्वनि विकृति को कम करने के लिए

- आधा घटाव होता है प्रोसेसर के ALU में उपयोग किया जाता है

- इसका उपयोग ऑपरेटरों को बढ़ाने और घटाने के लिए किया जा सकता है और पते की गणना भी कर सकता है

- आधा घटाव का उपयोग कम से कम महत्वपूर्ण स्तंभ संख्याओं को घटाने के लिए किया जाता है। बहु-अंकों की संख्या के घटाव के लिए, इसका उपयोग एलएसबी के लिए किया जा सकता है।

इसलिए, उपरोक्त आधे सबट्रैक्टर सिद्धांत से, अंत में, हम बंद कर सकते हैं कि इस सर्किट का उपयोग करके हम अंतर और बॉरो जैसे आउटपुट प्रदान करने के लिए एक बाइनरी बिट को दूसरे से घटा सकते हैं। इसी तरह, हम NAND गेट सर्किट के साथ-साथ NOR गेट्स का उपयोग करके आधा सबट्रैक्टर डिजाइन कर सकते हैं। ज्ञात की जाने वाली अन्य अवधारणाएँ क्या हैं आधा घटाव verilog कोड और RTL योजनाबद्ध आरेख कैसे तैयार किया जा सकता है?