एक युग था, जहां कंप्यूटर आकार में इतने विशाल थे कि उन्हें स्थापित करने के लिए, आसानी से एक कमरे की जगह की आवश्यकता होती थी। लेकिन आज वे इतने विकसित हैं कि हम उन्हें आसानी से नोटबुक के रूप में भी ले जा सकते हैं। जिस नवाचार ने इसे संभव बनाया वह इंटीग्रेटेड सर्किट की अवधारणा थी। में एकीकृत सर्किट , सक्रिय की एक बड़ी संख्या और निष्क्रिय तत्व उनके अंतर्संबंधों के साथ क्रॉस सेक्शन में आमतौर पर 50 से 50 मील की दूरी पर एक छोटे सिलिकॉन वेफर पर विकसित किया जाता है। इस तरह के सर्किट के उत्पादन के लिए मूल प्रक्रियाओं में एपिटैक्सियल ग्रोथ, मास्किंग अशुद्धता प्रसार, ऑक्साइड विकास और ऑक्साइड नक़्क़ाशी, पैटर्न बनाने के लिए फोटोलिथोग्राफी का उपयोग करना शामिल है।

वेफर के घटकों में प्रतिरोधक, ट्रांजिस्टर, डायोड, कैपेसिटर आदि शामिल हैं। आईसी के निर्माण के लिए सबसे जटिल तत्व ट्रांजिस्टर हैं। ट्रांजिस्टर विभिन्न प्रकार के होते हैं जैसे कि CMOS, BJT, FET। हम आवश्यकताओं के आधार पर एक आईसी के ऊपर कार्यान्वित होने के लिए ट्रांजिस्टर तकनीक का प्रकार चुनते हैं। इस लेख में आइए हम इस अवधारणा से परिचित हों CMOS निर्माण (या) CMOS के रूप में ट्रांजिस्टर का निर्माण।

CMOS निर्माण

कम बिजली अपव्यय आवश्यकता के लिए CMOS तकनीक ट्रांजिस्टर को लागू करने के लिए उपयोग किया जाता है। अगर हमें तेज सर्किट की आवश्यकता होती है तो ट्रांजिस्टर को लागू किया जाता है का उपयोग कर आईसी BJT । का निर्माण CMOS ट्रांजिस्टर जैसा कि आईसी तीन अलग-अलग तरीकों से किया जा सकता है।

एन-वेल / पी-वेल टेक्नोलॉजी, जहां एन-टाइप डिफ्यूजन एक पी-टाइप सब्सट्रेट पर किया जाता है या पी-टाइप डिफ्यूजन क्रमशः एन-टाइप सब्सट्रेट पर किया जाता है।

जुड़वां अच्छी तकनीक , कहां है NMOS और PMOS ट्रांजिस्टर एक सब्सट्रेट के बजाय एक एपिटैक्सियल ग्रोथ बेस पर एक साथ प्रसार द्वारा वेफर के ऊपर विकसित किया जाता है।

इंसुलेटर प्रक्रिया पर सिलिकॉन, जहां सब्सट्रेट के रूप में सिलिकॉन का उपयोग करने के बजाय एक इन्सुलेटर सामग्री का उपयोग गति और कुंडी-अप संवेदनशीलता को बेहतर बनाने के लिए किया जाता है।

एन-वेल / पी- वेल टेक्नोलॉजी

CMOS दोनों को एकीकृत करके प्राप्त किया जा सकता है NMOS और PMOS ट्रांजिस्टर एक ही सिलिकॉन वेफर पर। एन-वेल टेक्नॉलॉजी में एक एन-टाइप कुएं को पी-टाइप सब्सट्रेट पर अलग किया जाता है जबकि पी में अच्छी तरह से यह वाइस-वर्स है।

CMOS निर्माण कदम

CMOS निर्माण प्रक्रिया बहे एन-वेल / पी-वेल तकनीक का उपयोग करते हुए निर्मित बीस बुनियादी निर्माण चरणों का उपयोग किया जाता है।

अच्छी तरह से उपयोग कर CMOS बनाना

चरण 1: पहले हम निर्माण के लिए आधार के रूप में एक सब्सट्रेट चुनते हैं। एन- अच्छी तरह से, एक पी-प्रकार सिलिकॉन सब्सट्रेट का चयन किया जाता है।

सब्सट्रेट

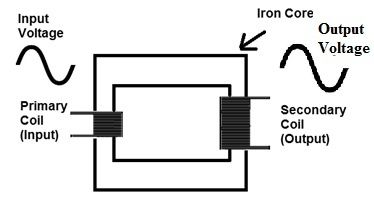

चरण 2 - ऑक्सीकरण: एन-प्रकार की अशुद्धियों का चयनात्मक प्रसार एक अवरोध के रूप में SiO2 का उपयोग करके पूरा किया जाता है जो सब्सट्रेट के संदूषण के खिलाफ वेफर के कुछ हिस्सों को बचाता है। सी.आई.ओ.दोलगभग 1000 पर ऑक्सीकरण कक्ष में उच्च-गुणवत्ता वाले ऑक्सीजन और हाइड्रोजन को सब्सट्रेट को उजागर करने के लिए किया गया ऑक्सीकरण प्रक्रिया द्वारा निर्धारित किया जाता है०सी

ऑक्सीकरण

चरण 3 - फोटोग्राफर की बढ़ती: इस स्तर पर चयनात्मक नक़्क़ाशी की अनुमति देने के लिए, SiO2 परत को फोटोलिथोग्राफ़ी प्रक्रिया के अधीन किया जाता है। इस प्रक्रिया में, वेफर को एक प्रकाश संश्लेषक पायस की एक समान फिल्म के साथ लेपित किया जाता है।

Photoresist की बढ़ती

चरण 4 - मास्किंग: यह कदम फोटोलिथोग्राफी प्रक्रिया की निरंतरता है। इस चरण में, स्टेंसिल का उपयोग करके खुलेपन का एक वांछित पैटर्न बनाया जाता है। इस स्टैंसिल का उपयोग फोटोरेसिस्ट के ऊपर मास्क के रूप में किया जाता है। सब्सट्रेट अब के संपर्क में है पराबैंगनी किरणों मुखौटे के उजागर क्षेत्रों के तहत मौजूद फोटोरिस्ट को पॉलीमराइज़ किया जाता है।

Photoresist की मास्किंग

चरण 5 - अप्रकाशित फ़ोटोग्राफ़र को हटाना: मुखौटा हटा दिया जाता है और ट्रिक्लोरोइथीलीन जैसे एक रसायन का उपयोग करके वेफर विकसित करके फोटोरेसिस्ट के अप्रकाशित क्षेत्र को भंग कर दिया जाता है।

फोटोरिस्ट का निष्कासन

चरण 6 - नक़्क़ाशी: वेफर हाइड्रोफ्लोरिक एसिड के एक नक़्क़ाशीदार समाधान में डूबा हुआ है, जो उन क्षेत्रों से ऑक्साइड को हटाता है जिनके माध्यम से डोपेंट को विसरित किया जाना है।

SiO2 की नक़्क़ाशी

चरण 7 - पूरे फोटोग्राफ़ी परत को हटाना: दौरान नक़्क़ाशी की प्रक्रिया , SiO2 के उन हिस्सों को जो फोटोरसिस्ट परत द्वारा संरक्षित हैं, प्रभावित नहीं होते हैं। फोटोरेसिस्ट मास्क को अब एक रासायनिक विलायक (गर्म H2SO4) के साथ निकाल दिया जाता है।

फोटोरिस्ट लेयर को हटाना

चरण 8 - एन-वेल का गठन: एन-प्रकार की अशुद्धियों को पी-प्रकार सब्सट्रेट में फैलाया जाता है जो कि उजागर क्षेत्र के माध्यम से होता है और इस प्रकार एक एन-वेल बनता है।

एन-वेल का गठन

चरण 9 - SiO2 को हटाना: SiO2 की परत अब हाइड्रोफ्लोरिक एसिड का उपयोग करके हटा दी जाती है।

SiO2 को हटाना

चरण 10 - पॉलीसिलिकॉन का जमाव: एक के गेट के misalignment CMOS ट्रांजिस्टर अवांछित कैपेसिटेंस को बढ़ावा देगा जो सर्किट को नुकसान पहुंचा सकता है। तो इसे रोकने के लिए 'स्व-संरेखित गेट प्रक्रिया' को प्राथमिकता दी जाती है जहां स्रोत के गठन से पहले गेट क्षेत्रों का गठन किया जाता है और आयन आरोपण का उपयोग करके नाली।

Polysilicon का जमाव

गेट के निर्माण के लिए पॉलीसिलिकॉन का उपयोग किया जाता है क्योंकि यह 8000 से अधिक उच्च तापमान का सामना कर सकता है०सी जब एक वेफर स्रोत और नाली के गठन के लिए एनालिंग विधियों के अधीन होता है। पॉलीसिलिकॉन का उपयोग करके जमा किया जाता है रासायनिक जमाव प्रक्रिया गेट ऑक्साइड की एक पतली परत पर। पॉलीसिलिकॉन परत के तहत यह पतला गेट ऑक्साइड गेट क्षेत्र के तहत आगे डोपिंग को रोकता है।

चरण 11 - गेट क्षेत्र का गठन: गेट के गठन के लिए आवश्यक दो क्षेत्रों को छोड़कर NMOS और PMOS ट्रांजिस्टर पॉलीसिलिकॉन के शेष हिस्से को छीन लिया गया है।

गेट क्षेत्र का गठन

चरण 12 - ऑक्सीकरण प्रक्रिया: एक ऑक्सीकरण परत वफ़र पर जमा होती है जो आगे के लिए ढाल के रूप में कार्य करती है प्रसार और धातुरूप करने की प्रक्रिया ।

ऑक्सीकरण प्रक्रिया

चरण 13 - मास्किंग और प्रसार: मास्किंग प्रक्रिया का उपयोग करके एन-प्रकार की अशुद्धियों के प्रसार के लिए क्षेत्र बनाने के लिए छोटे अंतराल बनाए जाते हैं।

मास्किंग

प्रसार प्रक्रिया का उपयोग करते हुए एनएमओएस के टर्मिनलों के गठन के लिए तीन एन + क्षेत्रों का विकास किया जाता है।

एन-डिफ्यूजन

चरण 14 - ऑक्साइड को हटाना: ऑक्साइड की परत छीन ली जाती है।

ऑक्साइड को हटाना

चरण 15 - पी-प्रकार का प्रसार: पीएमओएस पी-प्रकार के प्रसार के टर्मिनलों के गठन के लिए एन-प्रकार के प्रसार के समान है।

P- टाइप डिफ्यूजन

चरण 16 - मोटे क्षेत्र के ऑक्साइड का बिछाना: धातु के टर्मिनलों को बनाने से पहले एक मोटे क्षेत्र ऑक्साइड को वफ़र के क्षेत्रों के लिए एक सुरक्षात्मक परत बनाने के लिए बिछाया जाता है, जहाँ कोई टर्मिनलों की आवश्यकता नहीं होती है।

मोटी फील्ड ऑक्साइड परत

चरण 17 - धातुकरण: इस चरण का उपयोग धातु के टर्मिनलों के निर्माण के लिए किया जाता है जो आपस में जुड़ाव प्रदान कर सकते हैं। एल्यूमीनियम पूरे वफ़र पर फैला हुआ है।

धातुरूप करने की क्रिया

चरण 18 - अतिरिक्त धातु को हटाना: अतिरिक्त धातु को वेफर से हटा दिया जाता है।

चरण 19 - टर्मिनलों का गठन: इंटरकनेक्ट के लिए अतिरिक्त धातु टर्मिनलों को हटाने के बाद गठित अंतराल में।

टर्मिनलों का गठन

चरण 20 - टर्मिनल नाम निर्दिष्ट करना: के टर्मिनलों को नाम दिए गए हैं NMOS और PMOS ट्रांजिस्टर ।

टर्मिनल नाम निर्दिष्ट करना

P अच्छी तरह से Technology का उपयोग करके CMOS बनाना

पी-वेल प्रक्रिया एन वेल प्रक्रिया के समान है, सिवाय इसके कि यहां एन-टाइप सब्सट्रेट का उपयोग किया जाता है और पी-टाइप डिफ्यूज़न किया जाता है। सादगी के लिए आमतौर पर, एन अच्छी प्रक्रिया पसंद की जाती है।

CMOS की ट्विन ट्यूब फैब्रिकेशन

ट्विन-ट्यूब प्रक्रिया का उपयोग करके पी और एन-प्रकार के उपकरणों के लाभ को नियंत्रित किया जा सकता है। में शामिल विभिन्न कदम CMOS का निर्माण ट्विन-ट्यूब विधि का उपयोग करना इस प्रकार हैं

- एक हल्के से डोपेड एन या पी-टाइप सब्सट्रेट लिया जाता है और एपिटैक्सियल परत का उपयोग किया जाता है। एपिटैक्सियल परत चिप में कुंडी-अप समस्या से बचाती है।

- मापा मोटाई और सटीक डोपेंट एकाग्रता के साथ उच्च शुद्धता वाले सिलिकॉन परतों को उगाया जाता है।

- पी और एन कुएं के लिए ट्यूबों का गठन।

- प्रसार प्रक्रियाओं के दौरान संदूषण से सुरक्षा के लिए पतला ऑक्साइड निर्माण।

- आयन आरोपण विधियों का उपयोग करके स्रोत और नाली का निर्माण किया जाता है।

- धातु संपर्क के लिए भागों को बनाने के लिए कटौती की जाती है।

- धातु संपर्कों को आकर्षित करने के लिए धातुकरण किया जाता है

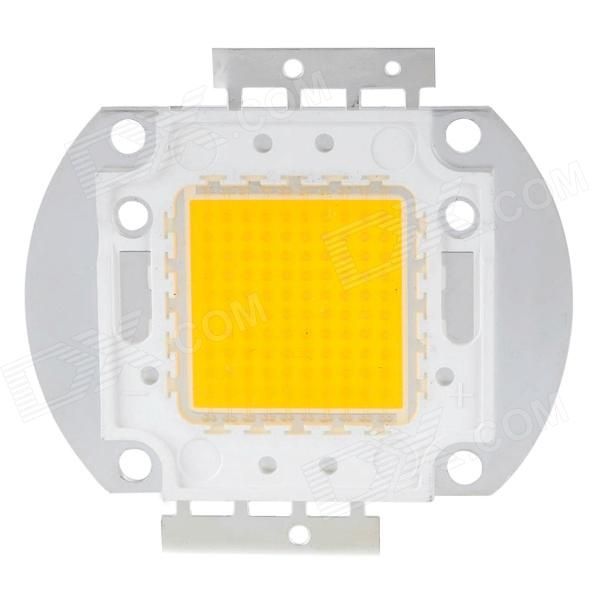

CMOS आईसी लेआउट

का ऊपरी दृश्य CMOS के लिए निर्माण और लेआउट दिया हुआ है। यहां विभिन्न धातु संपर्क और एन अच्छी तरह से अंतर स्पष्ट रूप से देखे जा सकते हैं।

CMOS आईसी लेआउट

इस प्रकार, यह सब के बारे में है CMOS निर्माण तकनीक । आइए एक 1-इन-स्क्वायर वेफर पर विचार करें जो सतह के 400 चिप्स को 50 मील की दूरी पर 50 मील की दूरी पर विभाजित करता है। एक ट्रांजिस्टर बनाने के लिए 50 मील 2 का क्षेत्र लगता है। इसलिए प्रत्येक IC में 2 ट्रांजिस्टर होते हैं और इस प्रकार 2 x 400 = 800 ट्रांजिस्टर होते हैं जो प्रत्येक वेफर पर निर्मित होते हैं। यदि प्रत्येक बैच में 10 वेफर्स संसाधित किए जाते हैं तो 8000 ट्रांजिस्टर एक साथ निर्मित किए जा सकते हैं। आईसी पर आपके द्वारा देखे गए विभिन्न घटक क्या हैं?